|

|

|

|

ASIC/FPGA Design and Verification Out Source Services

A simple system C test-bench for an AIS detect DUT

- For me system C is a great, license-free and high performance hardware simulator with the C++ as a verification engine.

- The purpose of this verification project is to verify an AIS detect DUT. The DUT detects AIS as explained below:

- The DUT declares an AIS if there are less than two zero bits in last two sequences of 512 bits in an input stream.

- The input stream is recieved via a simple interface: data byte and data byte valid.

- Once getting into an AIS state, at least six zero bits out of the last 1024 input bits are required to exit a formerly declared AIS state.

- The test bench is built of the following verification modules:

- Since the DUT interface is fairly simple, there is no seperate layer responsible for collecting the data from the DUT. Instead data collection is done in the monitor module.

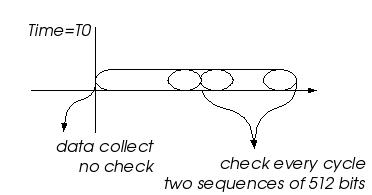

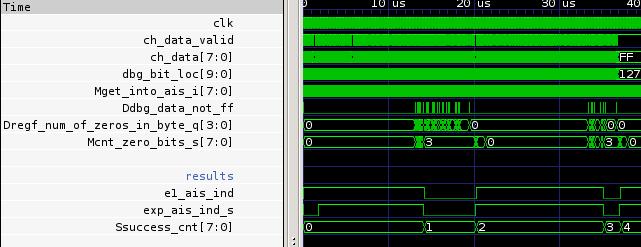

- This simple monitor has a single positive edge clock method. Data is collected and according to the detected state (AIS or not AIS) a decision is taken. After reset, the module waits for the appropriate bits of data to arrive and than checks every cycle on last collected 512 or 1024 bits.

- The monitor has also one non time consuming function, which calculates the number of zero bits in a given input data byte.

- The generator of the test bench generates the following items:

- It generates a clock for both DUT and the assorted modules in the test bench.

- It has a data generator, to generate specific cases of getting into AIS or out of AIS. This module was initially tested in a stand alone mode as described in

SCV data GEN SCV data GEN

- The scoreboard module checks that DUT data behaves in a same way as the expected data coming out of a reference model with the following features.

- Comparison made via a scoreboard to achieve a non cycle by cycle accurate DUT to expected test. This model of score boarding allows DUT design flexibility by self adjustment of the verification environement to DUT processing delay.

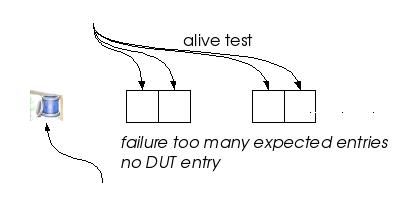

- Check alive mechanism. A simple counter implementation checks that both DUT and the expected AIS toggle. This is to say that each expected AIS state toggle must be followed by a DUT one.

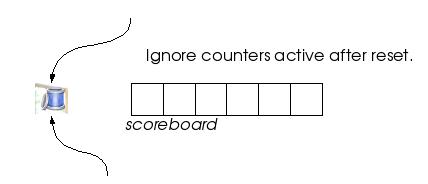

- A pair of ignore counters, with programmable startup values, to eliminate a possible false alarm, until DUT setup.

- Error report on failure and optionally a simulation stop the test on fatal error, saving disk space and simulation run time during regression. Once an error is detected, the simulation can be stopped after a programmable number of cycles.

- The sample module is a specific requirement of this very AIS detect DUT.

- The DUT is fully combinatorial. It is designed to be used in multiple places in the chip, with higher hierarchies of the design doing the sampling.

- The top's module task is to connect the assorted verification modules.

- The main runs the test and record waves.

- The systemc main module also handles the seed. If an argument is given on the command line, it is treated as seed otherwise a seed of one is used.

- Coverage is a way to tell if we have done enough tests during regression. The covergae specification for the AIS detect verilog DUT is explained in the following page: coverage.

- A regression script is also available at regression script.

- A regression how to run guide also exists at

coverage. coverage.

- The code is available at the download area. Look for the tar ball: pdh_ais_e1_m_main.cpp.gz.

|

Search This Site Search This Site

Feedback This Site Feedback This Site

new pages on this site new pages on this site

|

|