ASIC/FPGA Design and Verification Out Source Services

VHDL IP Stack

In this page I'll explain the simple test, which I did to quickly test the RX . This is as a first shot to understand the code.

- In this page I explain the transmit flow. The current test is an echo response. An echo response has been received and interpreted correctly and the core sends a response.

- First is the internet datagram sender component namely network layer send.

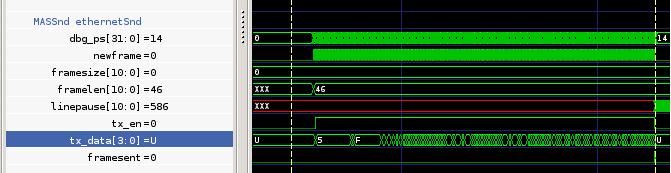

- The following waveform shows, that when send datagram is asserted, the component starts its work. At the end it outputs, to ETHERNET component, to send a packet (frame send command and frame size).

Press here to increase the picture Press here to increase the picture

- Since the ARP table is empty, the DUT sends an ARP in order to find the MAC address of the target IP.

Press here to increase the picture

The content of the ARP packet, as it is being built and send by the DUT, is in the following link. Press here to increase the picture

The content of the ARP packet, as it is being built and send by the DUT, is in the following link.

- As in the receive part, some minor changes had to be done to the code. This is because GHDL is probably more restricting with VHDL rules.

- First is library contention resolve:

use IEEE.std_logic_1164.all;

--use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_unsigned."+";

use IEEE.std_logic_unsigned."-";

- Some initializations on reset were added. The design is targeted to FPGA so it is good practice to do it anyway.

- Range fixing:

if cnt = datagramLen(10 downto 0) then

-

The checksum of the IP header from example is calculated in the following manner:

0x4500+0x0054+0xaafb+0x4000+0x0000+0xfc01+0x8b85+0xe902+0x8b85+0xd96e=0x505ca

0x5+0x05ca=0x05cf -> 0xfa30 checksum

Contact me now at: |