ASIC/FPGA Design and Verification Out Source Services

VHDL IP Stack

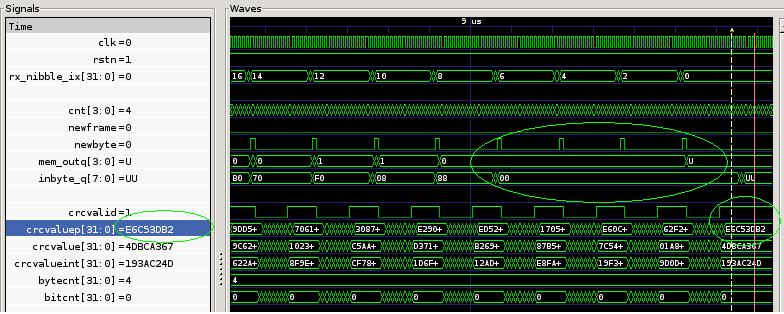

CRC test in a stand-alone dedicated test-bench.

- One thing I find very confusing is to figure out byte order and bit order, when calculating ETHERNET CRC. So it was in this case.

- I looked a bit in the Internet for some frames, which their CRC frame is calculated. One such site is : CRC example.

- I created a test-bench to inject the data. The test-bench instantiate the CRC from the VHDL IP stack project. I used a simple test-bench: no random, no multiple frame transmit.

- The data of the frame is captured into fields as shown below:

------------------------frame data------------------------

--MAC header

constant mac_dest : std_logic_vector (47 downto 0) := x"0010a47bea80";

constant mac_srce : std_logic_vector (47 downto 0) := x"001234567890";

constant mac_type : std_logic_vector (15 downto 0) := x"0800";

--IP ver 4 header

constant ipheader : std_logic_vector (95 downto 0) := x"4500002eb3fe000080110540";

constant ip_srcad : std_logic_vector (31 downto 0) := x"c0a8002c";

constant ip_dstad : std_logic_vector (31 downto 0) := x"c0a80004";

--ICMP header

constant icmptype : std_logic_vector ( 7 downto 0) := x"04";

constant icmpcode : std_logic_vector ( 7 downto 0) := x"00";

constant icmpcsum : std_logic_vector (15 downto 0) := x"0400";--checksum

constant icmpdata : std_logic_vector (207 downto 0) := x"001a2de8000102030405060708090a0b0c0d0e0f101100000000";

constant pkt_dlen : integer := 512; --length in bits

constant pkt_nlen : integer := pkt_dlen/4;--length in nibbles

--expected result from WEB 0xE6C53DB2

------------------------frame data------------------------

Note: When putting 00000000 at the frame end the CRC output is available. If, however, the CRC value, E6C53DB2, is used , we get 00000000 at CRC output.

- Some waveforms are in the following link:

waves Two cases are shown. Frame end padded with zeros. This is usually done at the transmit side to calculate a valid CRC. Frame with a correct CRC appended at the end as usually is the case in the receive side. A CRC of zero, indicates a frame a good frame reception. waves Two cases are shown. Frame end padded with zeros. This is usually done at the transmit side to calculate a valid CRC. Frame with a correct CRC appended at the end as usually is the case in the receive side. A CRC of zero, indicates a frame a good frame reception.

- The code is available in the following page: code

- When I worked on the CRC, I looked for numerical examples as much as a diver looks for oxygen, when he is under water. So here is another ICMP frame with a valid CRC: yet another example

Also avialable on this site (non free): An AHB VHDL project, built of two

AHB masters, one arbiter, one AHB to APB bridge and one simple APB slave.

If you are interested in this project as a graduate project, contact me

via mail and put in the subject: non free AHB project.

|