Simulation of the open cores 1G eth UDP / IP Stack using,the free VHDL simulator:

ghdl.

-

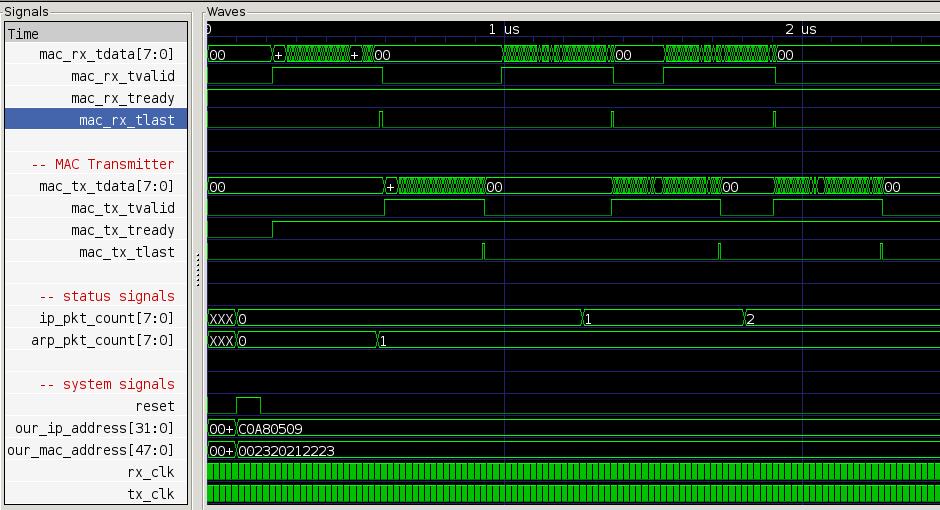

In search for self study projects for this site, I have downloaded from the open cores site, this

UDP project.

This project was also simulated with

cpp packet generator.

-

In this site, I use ghdl free simulator in many cases. The ghdl script for this project is a bit more complex. As opposed to the script used at

UART, the compilation command is different, because this project uses a few VHDL packages.

-

The script accepts a few parameters:

- #clear - removes the compilation directory before start

- #no_comp - skips compilation

- #vcd - run with vcd

- #200 - run 200 us. This is an optionally parameter. Default is 100 us.

-

VHDL packages are best handled automatically by the ghdl tool using a two step compilation scheme:

- ghdl -i --workdir=work --ieee=synopsys UDP_complete_nomac_tb.vhd ../../rtl/vhdl/*.vhd >& cmp.log

- grep vhd cmp.log > /dev/null

- if [ $? -eq 0 ] ; then

- echo "compilation failed"

- cat cmp.log

- exit 1

- else

- ghdl -m --workdir=work --ieee=synopsys UDP_complete_nomac_tb

- fi

-

I have placed the ghdl script in the test bench location:

udp_ip_stack/trunk/bench/vhdl

-

The version of code, which I downloaded, with the ghdl script, simulation log and waves in VCD format can be downloaded from:

udp code .

-

This VHDL DUT will be used to develop a self study verification project.

The verification will generate ARP or UDP packets, drive the packets to the DUT and check the DUT output.

The first step in creation this eVC verification project, is to design a UDP IP sequence item.

Some consideration in designing the sequence item are explained at:

link .

-

An initial version of the code, not fully compiled and tested, can downloaded from:

code .

-

This open core DUT and its test-bench was also compiled, using cadence ncvhdl tool. Please see the following:

link. .

|