ASIC/FPGA Design and Verification Out Source Services

SD VCD CRC7 Wave Flow.

In the SD verilog implementation only the restricted commands out of the

initialization is supported in the SD slave. The master supports the entire

initialization procedure and it will start reading some data from the slave.

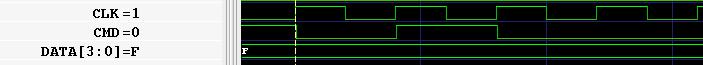

I'll describe the flow on the primary I/O only namely CLK and CMD.

Based on this free verilg SD version, a non free VHDL SD project

was created. It supports more SD commands like read burst, has a better

test-bench and a set of bash scripts to automate and randomize the

input stimuli.

The VHDL implementation uses

Samsung flash (k9f1208).

On time 100 there is a start bit following by a transmission one. Then the command CMD0 is placed on the command line, by the SD master, with CRC7 of 0x4A:Tx Command 0 0x00 parameter=0x00000000 data=0x400000000095

On time 3941 the paster issues another command namely: Tx Command 55 0x37 parameter=0x00000000 data=0x770000000065 The CRC7 for this command is 0x32.

The current slave is able to respond, currently, just to this command with R1 at time 7780: R1 response : Command 0x37. The CRC7 for the R1 response is 0x78. The R1 start is show below (start and transmit bits are 0).

The next picture shows the CRC7 of R1 followed by command 41. The command ends at 15780.

|