ASIC/FPGA Design and Verification Out Source Services

Post synthesis/NGD simulation

This page explains how to simulate a post NGD VHDL net-list.Once functional simulation ends, timing verification may help to determine if the design meets timing and performance requirement.

- First we open the VHDL net-list file, which was previously generated during the NGD step.

- The net-list uses the following library from XILINX: library UNISIM; So we need to compile it by GHDL simulator.

-

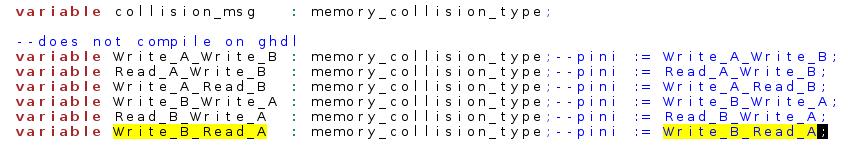

UNISIM library files don't compile with GHDL. So I copy the original files and slightly modified one file. The file unisim_VITAL.vhd requires some minor changes. Please note changing vendor libraries is bad practice.

This change is required in a few places. This change is required in a few places.

- The xilinx unisim library compile-script is the following unisim compile link.

- To compile the test-bench files including the memory model and the XILINX generated VHDL net-list, see the following test-bench compile link.

- After the simulation ends, there are a few topics to consider: visual inspection of VCD waves, compare transmit data of the current post synthesis (NGD) simulation with the one of the RTL and CPU run time.

- Visual inspection of the VCD wave is first done only for the primary outputs. I noticed that the DUT does not transmit any data. This can be the result of:

Some violation caused an X on some internal device in the VHDL net-list.

An error in synthesis or NGD process breaks the DUT.

GHDL is free simulator and sometimes, although very rare, it malfunctions. Also bear in mind that we had to modify the UNISIM library.

Other reason.

The first thing to debug is to fire up the keep hierarchy option both for XST synthesis and the NGD step, which follows:

"-keep_hierarchy YES" for XST constraint file.

- Usually the problem is in the test-bench. This was the case this time too. One of the inputs in the test-bench connected to DUT was not initialized and the X propagated and stalled the DUT. The fix was easy and is shown below:signal rx_dv_b : std_logic := '0';

-

Last it is interesting to note the CPU run-time taken for compilation and simulation at RTL and for the post-synthesis (NGD) net-list. From the synthesis report, the following line gives an estimation on the number of flip-flop devices.

Number of Slice Flip Flops: 1448

compilation

post NGD RTL

real 1m 0.051s 0m6.100s

user 0m40.670s 0m3.000s

sys 0m17.880s 0m3.030s

simulation

1m45.282s 0m6.450s

1m43.770s 0m5.410s

0m 0.560s 0m0.540s

To go back to the main page: VHDL IP top

To go to post layout gate-level + SDF simulation page: post PAR sim

Contact me now at: |