ASIC/FPGA Design and Verification Out Source Services

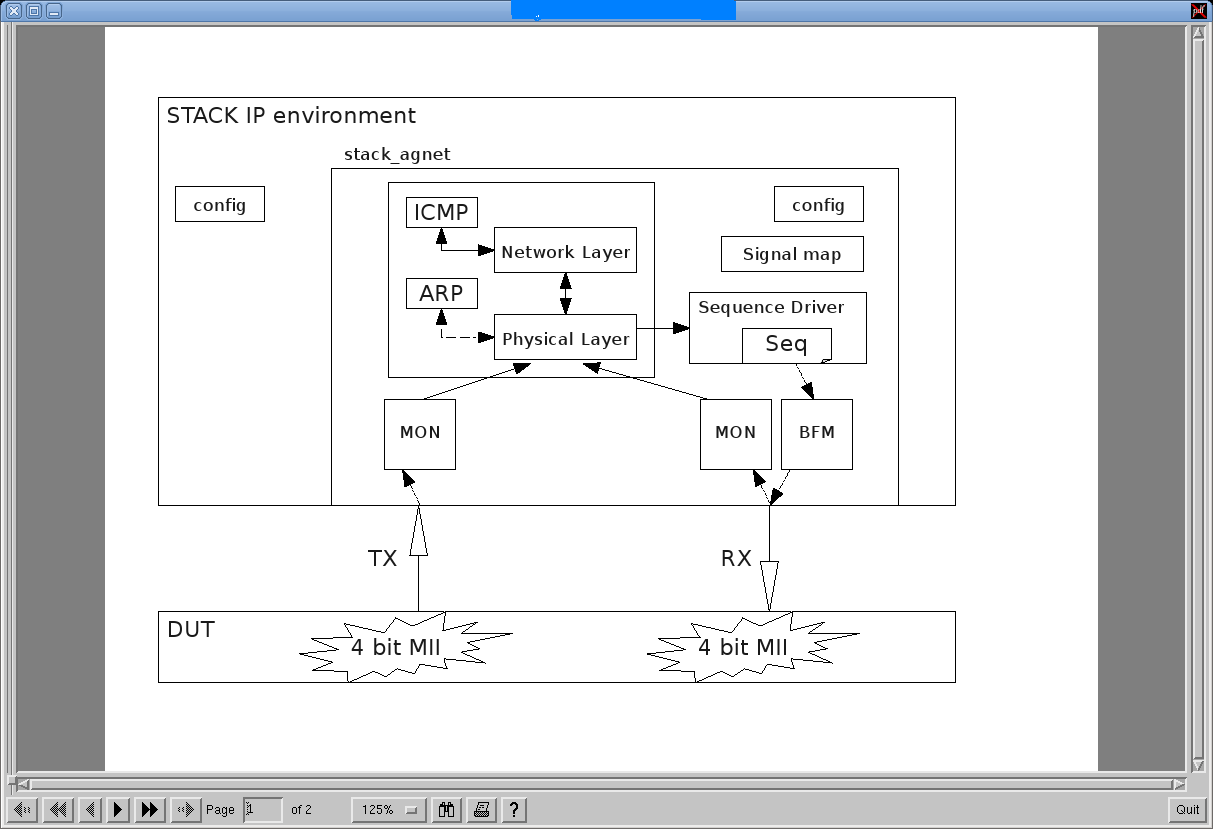

VHDL IP Stack Verification block diagram

Verifying the VHDL IP stack using specman:

- The following describes a general block diagram for verification of the STACK IP.

- The interface to the DUT both in transmit and receive side is 4 bit MII.

- On the receive side a sequence drives packets to the DUT via a BFM.

-

The generation flow is as follows:

The environment generates a ping request. Than network layer data is added. Based on formerly prepared ICMP

ICMP and network data, a physical layer frame is built and sent via MII.

The DUT may issue an ARP request. In that case the environment will check its validity and respond it.

The environment also checks the ICMP response coming out from the DUT. ICMP and network data, a physical layer frame is built and sent via MII.

The DUT may issue an ARP request. In that case the environment will check its validity and respond it.

The environment also checks the ICMP response coming out from the DUT.

-

The data item used in this verification component represents an ETHNERNET frame.

A structure to capture the ICMP assorted fields and a structure for ARP ones are defined.

Finally a structure to be used by the sequence driver, which also uses the above two structures as well as other fields to drive data to the DUT, is defined.

-

The next page describes the assorted files in this project:

files files

- Verification code development Plan for the VHDL IP stack project is at the following link:

V plan V plan

- How to compile the specman code and the VHDL DUT and test-bench code is described in the following guide. The compilation, elaboration and simulation is done using NCVHDL simulator.

run script run script

- IP frame checksum calculation is explained in

specman method that calculates the IP header checksum . specman method that calculates the IP header checksum .

- To go back to the VHDL IP main page:

main . main .

|