ASIC/FPGA Design and Verification Out Source Services

Cyclic buffer

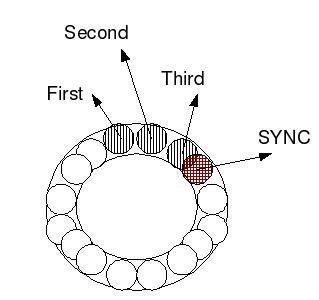

- The cyclic buffer is an array of fixed size.

- The size is set so that the buffer can absorb all the incoming data, till DUT gets into synchronized state.

- Each message is written in next location modulo size, which is to say: first message is placed on 0, second on N, ...size - N, 0, ....

- Once synchronized state is entered, each new message must be located at N bytes a way from former message.

Pros  and Cons and Cons

Simple to program. Simple to program. Simple to connect (connect pointers). Simple to connect (connect pointers). Same memory consumption for all states - synchronized state requires less memory. Same memory consumption for all states - synchronized state requires less memory.

Contact me now at: |