ASIC/FPGA Design and Verification Out Source Services

Simple multiplier and a test-bench in system C.

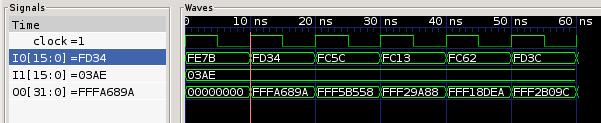

- For an FFT project I need a multiplier. The following is a simple multiplier.

- Once the timing and assorted bus width for all internal signals are resolved, for the FFT, this model will be replaced by synthesize-able one.

- A test-bench is also included to test multiplier.

- The input stimuli is driven from a fixed size array:

/*

dbg_mult 00000000 0000 03ae

dbg_mult fffa689a fe7b 03ae

dbg_mult fff5b558 fd34 03ae

dbg_mult fff29a88 fc5c 03ae

dbg_mult fff18dea fc13 03ae

dbg_mult fff2b09c fc62 03ae

dbg_mult fff5d2c8 fd3c 03ae

dbg_mult 00000000 0000 03ae

*/

void gen_p() {

const sc_int<16> d0[]={

0x0000, 0xfe7b, 0xfd34, 0xfc5c,

0xfc13, 0xfc62, 0xfd3c, 0x0000

};

const sc_int<16> d1[]={

0x03ae, 0x03ae, 0x03ae, 0x03ae,

0x03ae, 0x03ae, 0x03ae, 0x03ae

};

I0.write(d0[p.read()]);

I1.write(d1[p.read()]);

sc_uint<8> pw=(p.read()+1)%8;

if(p.read() == 7) sc_stop();

p.write(pw);

...

- The code is in the download area. Look for the file SCmult.tar.gz.

The code can be directly downloaded from: code

The code can be directly downloaded from: code

Contact me now at: |