ASIC/FPGA Design and Verification Out Source Services

This is a scoreboard written e (specman).

In this example I show a simple scoreboard. It is build of two lists of bit: one for the input and the other one for the output.

It also contains a dedicated compare method. The requirements from the compare method are:

The output may be up to one cycle delayed from the input.

Initially the compare works in not synchronized mode, where it just expects all bits to be zero. This mode can be overwritten and it can be initialized to start in synchronize mode.

If either the input or output receives a single non zero bit, the compare method tries to match between the input and output, allowing one cycle difference if exists.

If match was found by the compare method, synchronized state is declared. In this state, data has to be always the same for every 16 bits of data collection. This is to say no one cycle delay tolerant is acceptable any more.

Compare is called, after 16 bits of input and output, have been collected.

After compare method ends its check, data is cleared from each list, based on the match delay between the streams (0 or 1 cycle).

In the beginning, when in not synchronized state, if all buffer, 16 bits list, is entirely zero, it simply cleared:

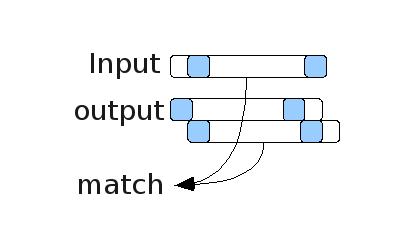

Once synchronized state is achieved (the example below shows a one cycle delay between the streams):

Once synchronized state is achieved (the example below shows a one cycle delay between the streams):

Code explanation:

First is the main variables, which are used: to allow synchronization print once on entering the state.

Second is the synchronization state variable.

Last are the input and output lists.

cmp_sync_dbg : bool; --debug sync message print once on sync

keep soft cmp_sync_dbg == TRUE;

cmp_sync : bool;

keep soft cmp_sync == FALSE;

sbd_i : list of bit;

sbd_o : list of bit;

keep soft sbd_i.size() == 0;

keep soft sbd_o.size() == 0;

When not in synchronization state:

if(sbd_i.size() > 16) then {

skip_cmp=FALSE;

if(!cmp_sync) then {

if( sbd_i.all(it == 1).is_empty() ) then {

if( sbd_o.all(it == 1).is_empty() ) then {

sbd_i.clear(); sbd_o.clear();

skip_cmp=TRUE;

Once match is done, the lists have to be erased. In case where one cycle of delay does exist, between the stream, the job is not as easy as to clear the lists. The way it is done is shown below:

--if the former did not match, this one must, because only one cycle

--delay is allowed

sz = sbd_o.size()-2;

if(sbd_i[0..sz] == sbd_o[1..]) then {

cmp_sync=TRUE; sbd_o.clear(); sbd_i=sbd_i[sz+1..];

The most up-to-date version of the code can be taken from:

scoreboard e (specman) code

You may also be interested in:

example of back pressure temporal check

|