ASIC/FPGA Design and Verification Out Source Services

system C FFT data input first stage

- This code is part of 16 point FFT project.

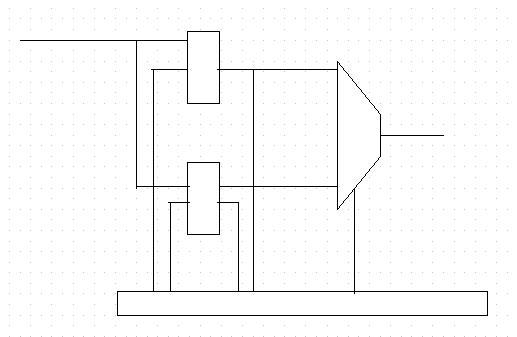

- This module is used as the first stage of the FFT. The purpose of the module is to store the input data. It is designed to allow concurrent input data buffering and output of former sample points to the first FFT computation stage.

- It uses two dual port RAM devices.The memory modules are also available in this site: DPRAM .

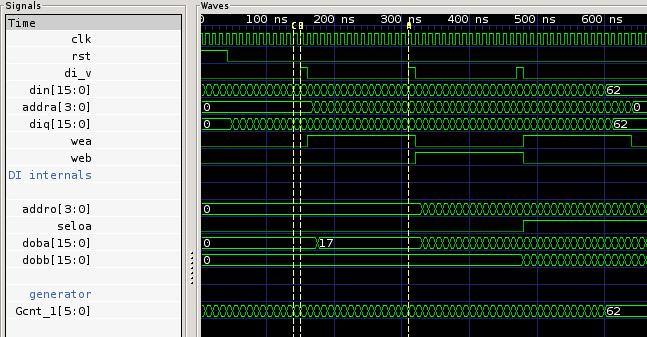

- Like in other system C small projects, available from this site, a test bench is also included.

- The test bench does not have an automatic checker. The code will be intensively tested in the FFT project and this test bench allows just a visual inspection via waves and log.

- Each module consists of two files: an header file and main block. See following short examples:

header header

main main

Project Makefile Project Makefile

- People who were interested in this site also wanted to see the page regarding complex multiplier. ...Usually such a design uses four multipliers. This design does it with only three multipliers... press here for complex Multiplier, but the best way to navigate and look around things in my site is to use the search my site option.

- The code is in the download area. Look for the file SCfft_di.tar.gz.

- Need to improve: The output address drives both memory devices while only on RAM is used. This simplifies the design, but consumes more power. Better to have a constant address value for the RAM, which is not used for data read.

Contact me now at: |