ASIC/FPGA Design and Verification Out Source Services

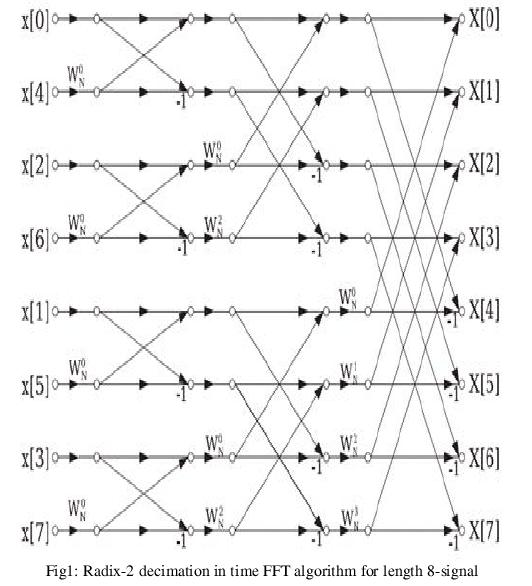

FFT system C project - 8 point FFT using DIT algorithm.

- This projects implements an eight point Decimation In Time Fast Fourier Transform.

- The internal data buses width and representation will be discussed and explained FFT design consideration .

- Twiddle factors representation is also described. For instance for the third stage FFT calculation, fractional numbers are required such as .070710678.see FFT Twiddle Factors

- The FFT also introduce some gain, which proportional to the number of points. This is discussed at FFT gain compensation .

- The accuracy of the implementation is also discussed reference to a C golden model FFT accuracy issues .

- Two reference models are used to verify the results, which are explained at FFT reference models

- The following commands and scripts were used to compile and run the FFT system C design FFT commands and scripts .

- The system C code is available for free FFT system C code . A VHDL version also exists.

- The algorithm, which is used, is shown below:

-

A complex multiplier (two-dimensional Cartesian coordinate is used at

both of its inputs and outputs)

using only three

scalar multipliers, to save chip area, is also available

on this site:

page.

-

Another project is an AHB VHDL project, made of two AHB masters, one arbiter,

one AHB to APB bridge and one simple APB slave. If you are interested in

this project as a graduate project,

contact me via mail and put in the subject: non free AHB project.

Please let me know what you think on this FFT work.

Contact me now at: |